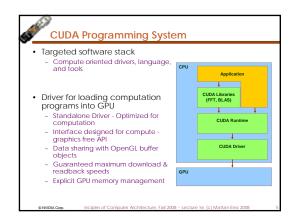

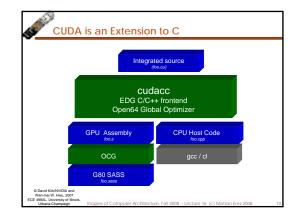

### CUDA API and Language: Easy and Lightweight

- The API is an extension to the ANSI C programming language

Low learning curve

- The hardware is designed to enable lightweight runtime and driver

- → High performance

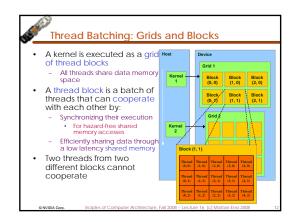

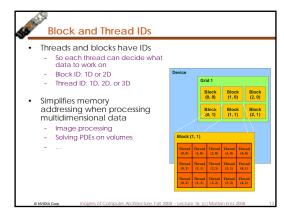

# CUDA Programming Model: A Highly Multithreaded Coprocessor

- The GPU is viewed as a compute device that:

\_ Is a coprocessor to the CPU or host

- Has its own DRAM (device memory)

- Runs many threads in parallel

- Data-parallel portions of an application are executed on the device as kernels which run in parallel on many threads

- Differences between GPU and CPU threads

GPU threads are extremely lightweight

- Very little creation overhead

- GPU needs 1000s of threads for full efficiency

- Multi-core CPU needs only a few

© David Kirk/NVIDIA and Wen-mei W. Hwu, 2007 ECE 498AL, University of Illinois,

| ß                                                                                                                                                   |                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| CUDA is an Extens                                                                                                                                   | sion to C                                                                                                                    |

| Declspecs     global, device, shared,                                                                                                               | device float filter[N];<br>global void convolve (float *image) {                                                             |

| local, constant Keywords – threadldx, blockldx Intrinsics –syncthreads                                                                              | shared float region[M];<br><br>region[threadIdx] = image[i];<br>syncthreads()                                                |

| Runtime API     Memory, symbol,     execution     management                                                                                        | <pre>image[j] = result; } // Allcoate GBU memory void *myimage = cudsMalloc(bytes) // 100 blocks, 10 threads per block</pre> |

| Function launch     David KirkNVIDIA and     Wen-mei W. Hwu, 2007 ECE 49RAL, University of linais,     Ubban-Champaign     inciples of Computer Arc | convolve<<<100, 10>>> (myimage);<br>chitecture, Fall 2008 - Lecture 16 (c) Mattan Frez 2008 111                              |

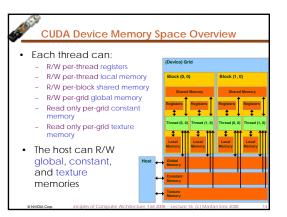

# Access Times

- Register dedicated HW single cycle

- Shared Memory dedicated HW two cycles

- Hidden by warps

- Local Memory DRAM, no cache \*slow\*

- Global Memory DRAM, no cache \*slow\*

- Constant Memory DRAM, cached, 1...10s...100s of cycles, depending on cache locality

- Texture Memory DRAM, cached, 1...10s...100s of cycles, depending on cache locality

- Instruction Memory (invisible) DRAM, cached

Wen-mei W. Hwu, 2007 ECE 498AL, University of Illinois,

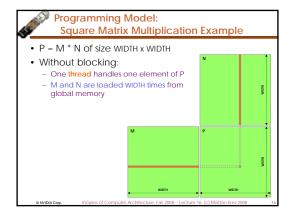

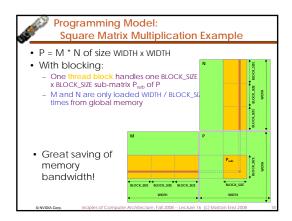

# Programming Model: Common Programming Pattern

- Local and global memory reside in device memory (DRAM) - much slower access than shared memory

– Uncached

- So, a common way of scheduling some computation on the device is to block it up to take advantage of fast shared memory:

- Partition the data set into data subsets that fit into shared memory

- Handle each data subset with one thread block by:

Loading the subset from global memory to shared memory

Performing the computation on the subset from shared memory: each thread can efficiently multi-pass over any data element

- Copying results from shared memory to global memory

## A quick review

- device = GPU = set of multiprocessors

- Multiprocessor = set of processors & shared memory

- Kernel = GPU program

NVIDIA Co

- Grid = array of thread blocks that execute a kernel

- Thread block = group of SIMD threads that execute a kernel and can communicate via shared memory

| Memory   | Location | Cached | Access     | Who                       |

|----------|----------|--------|------------|---------------------------|

| Local    | Off-chip | No     | Read/write | One thread                |

| Shared   | On-chip  | N/A    | Read/write | All threads in a<br>block |

| Global   | Off-chip | No     | Read/write | All threads + host        |

| Constant | Off-chip | Yes    | Read       | All threads + host        |

| Texture  | Off-chip | Yes    | Read       | All threads + host        |

# CUDA: C on the GPU

- A simple, explicit programming language solution

- Extend only where necessary

- \_\_global\_\_ void KernelFunc(...);

- \_\_shared\_\_ int SharedVar;

- KernelFunc<<< 500, 128 >>>(...);

- Explicit GPU memory allocation

cudaMalloc(), cudaFree()

- Memory copy from host to device, etc.

- cudaMemcpy(), cudaMemcpy2D(),...

© NVIDIA Corp. Inciples of Computer Architecture, Fall 2008 -- Lecture 16 (c) Mattan Erez 2008

# Example: Vector Addition Kernel

// Pair-wise addition of vector elements

// One thread per addition

### <u>\_\_global\_\_</u> void

NVIDIA C

vectorAdd(float\* iA, float\* iB, float\* oC)

int idx = threadIdx.x + blockDim.x \* blockId.x; oC[idx] = iA[idx] + iB[idx];

Example: Vector Addition Host Code

float\* h\_A = (float\*) malloc(N \* sizeof(float));

float\* h\_B = (float\*) malloc(N \* sizeof(float));

// ... initalize h\_A and h\_B

// allocate device memory

float\* d\_A, d\_B, d\_C;

cudaMalloc( (void\*\*) &d\_A, N \* sizeof(float)));

cudaMalloc( (void\*\*) &d\_B, N \* sizeof(float)));

cudaMalloc( (void\*\*) &d\_C, N \* sizeof(float)));

// copy host memory to device cudaMemcpy( d\_A, h\_A, N \* sizeof(float), cudaMemcpyHostDoevice) ); cudaMemcpy( d\_B, h\_B, N \* sizeof(float), cudaMemcpyHostToDevice) );

// execute the kernel on N/256 blocks of 256 threads each vectorAdd<<< N/256, 256>>>( d\_A, d\_B, d\_C);

© NVIDIA Corp. Inciples of Computer Architecture, Fall 2008 -- Lecture 16 (c) Mattan Erez 2008

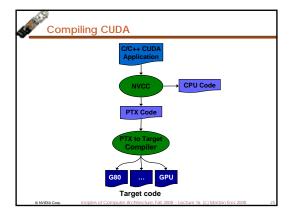

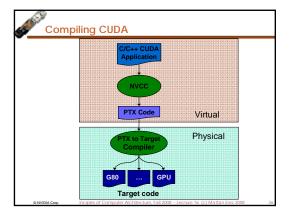

| Compila                                                                                                             | tion                                                                     |    |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----|

| extensions I<br>NVCC is a (<br>- Works by in<br>cudacc, g:<br>NVCC can<br>- Either C cor<br>· That mus<br>using and |                                                                          |    |

| <ul> <li>Any execut<br/>dynamic lik</li> <li>The CUDA r</li> </ul>                                                  | table with CUDA code requires two                                        |    |

| © NVIDIA Corp. incl                                                                                                 | ples of Computer Architecture, Fall 2008 Lecture 16 (c) Mattan Erez 2008 | 24 |

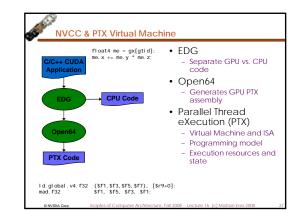

# Role of Open64

### Open64 compiler gives us

- A complete C/C++ compiler framework. Forward looking. We do not need to add infrastructure framework as our hardware arch advances over time.

- A good collection of high level architecture independent optimizations. All GPU code is in the inner loop.

- Compiler infrastructure that interacts well with other related standardized tools.

### Debugging Using the Device Emulation Mode

- An executable compiled in device emulation mode (nvcc -deviceemu) runs completely on the host using the CUDA runtime

- No need of any device and CUDA driver

- Each device thread is emulated with a host thread

- When running in device emulation mode, one can:

- Use host native debug support (breakpoints, inspection, etc.)

Access any device-specific data from host code and vice-

- Versa

- Call any host function from device code (e.g. printf) and vice-versa

- Detect deadlock situations caused by improper usage of \_\_\_\_syncthreads

- © NVIDIA Corp. Inciples of Computer Architecture, Fall 2008 -- Lecture 16 (c) Mattan Erez 20

### **Device Emulation Mode Pitfalls**

- Emulated device threads execute sequentially, so simultaneous accesses of the same memory location by multiple threads potentially produce different results

- Dereferencing device pointers on the host or host pointers on the device can produce correct results in device emulation mode, but will generate an error in device execution mode

- Results of floating-point computations will slightly differ because of:

- Different compiler outputs

- Different instruction sets

- Use of extended precision for intermediate results

- There are various options to force strict single precision on the host

# Parameterize Your Application

- Parameterization helps adaptation to different GPUs

- GPUs vary in many ways

- # of multiprocessors

- Shared memory size

- Register file size

- Threads per block

- Memory bandwidth

- You can even make apps self-tuning (like FFTW)

- "Experiment" mode discovers and saves optimal config

Mattan Erez EE382V: Principles of Computer Architecture, Fall 2008 -- Lecture 16 (c) Mattan Erez 2008

# CUDA Optimization Priorities Memory coalescing is #1 priority Highest I/S optimization Optimize for locality Iake advantage of shared memory Very high bandwidth Threads can cooperate to save work Use parallelism efficiently Keep the GPU busy at all times High arithmetic / bandwidth ratio Many threads & thread blocks Leave bank conflicts and divergence for last! - 4-way and smaller conflicts are not usually worth avoiding if avoiding them will cost more instructions

NVIDIA Co